Per Stenström Michel Dubois Manolis Katevenis Rajiv Gupta Theo Ungerer (Eds.)

# High Performance Embedded Architectures and Compilers

Third International Conference, HiPEAC 2008 Göteborg, Sweden, January 2008 Proceedings

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

# Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Per Stenström Michel Dubois Manolis Katevenis Rajiv Gupta Theo Ungerer (Eds.)

# High Performance Embedded Architectures and Compilers

Third International Conference, HiPEAC 2008 Göteborg, Sweden, January 27-29, 2008 Proceedings

#### Volume Editors

Per Stenström Chalmers University of Technology, Dept. of Computer Science and Engineering 412 96 Gothenburg, Sweden E-mail: pers@chalmers.se

Michel Dubois University of Southern California, Dept. of Electrical Engineering 3740 McClintock Ave., Los Angeles, CA 90089-2562, USA E-mail: dubois@paris.usc.edu

Manolis Katevenis FORTH-ICS 100 Plastira Ave., Vassilika Vouton, 70-013 Heraklion, Crete, Greece E-mail: kateveni@ics.forth.gr

Rajiv Gupta University of California, Riverside, Dept. of Computer Science and Engineering 408 Engineering Building II, Riverside, CA 92521, USA E-mail: gupta@cs.ucr.edu

Theo Ungerer University of Augsburg, Institute of Computer Science 86135 Augsburg, Germany E-mail: ungerer@informatik.uni-augsburg.de

Library of Congress Control Number: 2007942570

CR Subject Classification (1998): B.2, C.1, D.3.4, B.5, C.2, D.4

LNCS Sublibrary: SL 1 - Theoretical Computer Science and General Issues

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-540-77559-5 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-540-77559-1 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12212101 06/3180 543210

# Preface

The first two editions of the HiPEAC conference series in Barcelona (2005) and Ghent (2007) have really demonstrated that the topics covered by HiPEAC attract a lot of interest. In the 2007 conference, about 200 people attended the conference and its satellite events. The third HiPEAC conference was held in Göteborg, the second largest city in Sweden.

The offerings of this conference were rich and diverse. We offered attendees a set of four workshops on topics that are all central to the HiPEAC roadmap: multi-cores, compiler optimizations, reconfigurable computing, and interconnection networks. Additionally, a tutorial on the Sunflower Toolsuite was offered.

The conference program was as rich as in the last years. It featured many important and timely topics such as multi-core processors, reconfigurable systems, compiler optimization, power-aware techniques and more. The conference also offered a keynote speech by Mateo Valero – the Eckert-Mauchly Award winner in 2007. Several social events provided opportunities for interaction and exchange of ideas in informal settings such as a tour at the Universeum – a science exhibition center and aquarium – where the banquet took place as well.

This year we received 77 submissions of which 14 papers were Committee papers. Papers were submitted from 22 different nations (about 40% from Europe, 25% from Asia, 30% from North America and 5% from South America), which is a token of the global visibility of the conference.

We had the luxury of having a strong Program Committee consisting of 37 experts in all areas within the scope of the conference and we kept all reviewing within the Program Committee. Thus, each paper was typically reviewed by four Program Committee members. We collected 301 reviews and we were happy to note that each paper was rigorously reviewed before we made the decisions, despite the fact that we shortened the review phase and that reviewing took place during most reviewers' precious vacation time.

The Program Committee meeting was held in the center of Rome, the ancient capital of Italy. Despite a long trip for many members of the Program Committee, 16 PC members attended the meeting. For virtually all papers, at least two reviewers were present. The PC meeting was preceded by an e-mail discussion of papers among the reviewers. At the PC meeting the papers were discussed in the order of average score also including PC papers. When a paper was discussed where a participating PC member was either a co-author or had conflicts with that paper, that person left the room. We accepted 25 papers of which 4 are PC papers, yielding an acceptance rate of 32%.

The end result of the whole effort was the high-quality program for the HiPEAC 2008 event. We hope that you learn and get much inspiration from this proceedings volume.

The planning of a conference starts way ahead of the actual event. If it were not for the unselfish and hard work of a large number of devoted individuals, this conference would not have been as successful as it was. Let us first thank the authors for their great contributions which constitute the core of the conference. We were very fortunate to collect a great team to power this event and would like to thank all of them: Mats Brorsson (KTH) for putting together an attractive pre-conference program; Ewa Wäingelin (Chalmers) for the enormous effort she invested in the local arrangement; Per Waborg (Chalmers) for a fantastic job in keeping the costs within budget and running the books; Mike O'Boyle (Edinburgh) for timely publicity campaigns; Jörg Mische and Theo Ungerer (Augsburg) for the hard work in putting together the proceedings; Michiel Ronsee (Ghent) for administering the submission and review system; and finally Sylvie Detournay (Ghent) for administering the web. Thanks to all of you!

Finally, we would also like to mention the support from the Sixth Framework Programme of the European Union, represented by project officers Mercè Griera i Fisa and Panagiotis Tsarchopoulos, for sponsoring the event and for the travel grants.

October 2007

Per Stenström Michel Dubois Manolis Katevenis Rajiv Gupta

# Organization

# Executive Committee

| General Co-chairs           | Per Stenström                             |

|-----------------------------|-------------------------------------------|

|                             | Chalmers University of Technology, Sweden |

|                             | Michel Dubois                             |

|                             | University of Southern California, USA    |

| Program Committee Co-chairs | Manolis Katevenis                         |

|                             | University of Crete / FORTH, Greece       |

|                             | Rajiv Gupta                               |

|                             | University of California, Riverside, USA  |

| Workshop/Tutorials Chair    | Mats Brorsson                             |

|                             | KTH, Sweden                               |

| Local Arrangements Chair    | Ewa Wäingelin                             |

|                             | Chalmers University of Technology, Sweden |

| Finance Chair               | Per Waborg                                |

|                             | Chalmers University of Technology, Sweden |

| Publicity Chair             | Mike O'Boyle                              |

|                             | University of Edinburgh, UK               |

| Publications Chair          | Theo Ungerer                              |

|                             | University of Augsburg, Germany           |

| Submissions Chair           | Michiel Ronsse                            |

|                             | Ghent University, Belgium                 |

| Web Chair                   | Sylvie Detournay                          |

|                             | Ghent University, Belgium                 |

# **Program Committee**

| Angelos Bilas     |

|-------------------|

| Mats Brorsson     |

| Koen De Bosschere |

| Jack Davidson     |

| Marc Duranton     |

| Babak Falsafi     |

| Paolo Faraboschi  |

| Kristian Flautner |

| Chris Gniady      |

| Wen-mei Hwu       |

| Paolo Ienne       |

| Norm Jouppi       |

FORTH / University of Crete, Greece KTH, Sweden University of Ghent, Belgium University of Virginia, USA NXP Semiconductors, Netherlands Carnegie Mellon University, USA HP Labs, Spain ARM, UK University of Arizona, USA University of Arizona, USA EPFL, Switzerland HP Labs, USA

Mahmut Kandemir Stefanos Kaxiras Christos Kozvrakis Scott Mahlke Peter Marwedel Avi Mendelson Andreas Moshovos Mike O'Bovle Kunle Olukotun Yunheung Paek Santosh Pande Yale Patt Alex Ramirez Lawrence Rauchwerger John Regehr Andre Seznec Guri Sohi Olivier Temam Josep Torrellas Mateo Valero David Whalley Sudhakar Yalamanchili

# Steering Committee

Mateo Valero Anant Agarwal Koen De Bosschere Mike O'Boyle Brad Calder Rajiv Gupta Wen-mei W. Hwu Josep Llosa Margaret Martonosi Per Stenström Olivier Teman

# Reviewers

Minwook Ahn Mauricio Alvarez Sara Baghsorkhi Mauro Bianco Angelos Bilas Pennsylvania State University, USA University of Patras, Greece Stanford University, USA University of Michigan, USA University of Dortmund, Germany Intel. Israel University of Toronto, Canada Edinburgh University, UK Stanford University, USA Seoul National University, Korea Georgia Institute of Technology, USA University of Texas at Austin, USA UPC / BSC, Spain Texas A&M University, USA University of Utah, USA INRIA, France University of Wisconsin, USA INRIA, France University of Illinois, USA UPC / BSC, Spain Florida State University, USA Georgia Institute of Technology, USA

UPC / BSC, Spain MIT, USA Ghent University, Belgium University of Edinburgh, UK University of California, USA University of California, Riverside, USA UIUC, USA UPC, Spain Princenton University, USA Chalmers University of Technology, Sweden INRIA Futurs, France

Mauricio Breternitz Jr.Bruce ofMats BrorssonDoosarFelipe CabarcasMichaeFrancisco CazorlaRomainLuis CezeMichae

Bruce Childers Doosan Cho Michael Chu Romain Cledat Michele Co Albert Cohen Clark Coleman Adrian Cristal Jack Davidson Koen De Bosschere Marc Duranton Avose Falcon Babak Falsafi Kevin Fan Paolo Faraboschi Kristian Flautner Grigori Fursin Chris Gniady Daniel Gracia-Perez Brian Greskamp Jason Hiser Wen-mei Hwu Paolo Ienne Daniel Jimenez Jose Joao Norm Jouppi Mahmut Kandemir Stefanos Kaxiras DaeHo Kim Hokvun Kim Wonsub Kim Yongioo Kim Christos Kozyrakis Manjunath Kudlur Tushar Kumar Christopher Kung

Chang Joo Lee Jongwon Lee Piotr Lesnicki Yue Li Yongmo Liang Danny Lynch Scott Mahlke Peter Marwedel Mojtaba Mehrara Avi Mendelson Rustam Miftakhutdinov Pablo Montesinos Miquel Moreto Andreas Moshovos Gilles Mouchard Vevnu Narasiman Mike O'Boyle Kunle Olukotun Daniel Ortega Yunheung Paek Alex Pajuelo Santosh Pande Ioannis Papadopoulos Hyunchul Park Sanghyun Park Yale Patt Androniki Pazarloglou Maikel Pennings Antoniu Pop Alex Ramirez Lawrence Rauchwerger

John Regehr Christopher Rodrigues Shane Ryoo Esther Salami Fermin Sanchez Oliverio Santana Andre Seznec Tim Smith Guri Sohi Jaswanth Sreeram Santhosh Srinath Samuel Stone Karin Strauss M. Aater Suleman Gabriel Tanase Olivier Temam Nathan Thomas Abhishek Tiwari Josep Torrellas Sain-Zee Ueng Mateo Valero Javier Vera David Whalley Sudhakar Yalamanchili Sami Yehia Jonghee Youn Kun Zhang Hongtao Zhong

# Table of Contents

# Invited Program

| Supercomputing for the Future, Supercomputing from the<br>Past (Keynote)                                                                                                                                                         | 3  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Mateo Valero and Jesús Labarta                                                                                                                                                                                                   |    |

| I Multithreaded and Multicore Processors                                                                                                                                                                                         |    |

| MIPS MT: A Multithreaded RISC Architecture for Embedded<br>Real-Time Processing<br><i>Kevin D. Kissell</i>                                                                                                                       | 9  |

| rMPI: Message Passing on Multicore Processors with On-Chip<br>Interconnect<br>James Psota and Anant Agarwal                                                                                                                      | 22 |

| <ul> <li>Modeling Multigrain Parallelism on Heterogeneous Multi-core</li> <li>Processors: A Case Study of the Cell BE</li> <li>Filip Blagojevic, Xizhou Feng, Kirk W. Cameron, and</li> <li>Dimitrios S. Nikolopoulos</li> </ul> | 38 |

| IIa Reconfigurable - ASIP                                                                                                                                                                                                        |    |

| BRAM-LUT Tradeoff on a Polymorphic DES Design<br>Ricardo Chaves, Blagomir Donchev, Georgi Kuzmanov,<br>Leonel Sousa, and Stamatis Vassiliadis                                                                                    | 55 |

| Architecture Enhancements for the ADRES Coarse-Grained<br>Reconfigurable Array<br>Frank Bouwens, Mladen Berekovic, Bjorn De Sutter, and<br>Georgi Gaydadjiev                                                                     | 66 |

| Implementation of an UWB Impulse-Radio Acquisition and<br>Despreading Algorithm on a Low Power ASIP<br>Jochem Govers, Jos Huisken, Mladen Berekovic, Olivier Rousseaux,<br>Frank Bouwens, Michael de Nil, and Jef Van Meerbergen | 82 |

| IIb Compiler Optimizations                                                                                                                                                                                                       |    |

####

| Studying Compiler Optimizations on Superscalar Processors Through   |     |

|---------------------------------------------------------------------|-----|

| Interval Analysis                                                   | 114 |

| Stijn Eyerman, Lieven Eeckhout, and James E. Smith                  |     |

| An Experimental Environment Validating the Suitability of CLI as an |     |

| Effective Deployment Format for Embedded Systems                    | 130 |

| Marco Cornero, Roberto Costa, Ricardo Fernández Pascual,            |     |

| Andrea C. Ornstein, and Erven Rohou                                 |     |

# III Industrial Processors and Application Parallelization

| Compilation Strategies for Reducing Code Size on a VLIW Processor<br>with Variable Length Instructions | 147 |

|--------------------------------------------------------------------------------------------------------|-----|

| Todd T. Hahn, Eric Stotzer, Dineel Sule, and Mike Asal                                                 |     |

| Experiences with Parallelizing a Bio-informatics Program on the Cell                                   |     |

| BE                                                                                                     | 161 |

| Hans Vandierendonck, Sean Rul, Michiel Questier, and                                                   |     |

| Koen De Bosschere                                                                                      |     |

| Drug Design Issues on the Cell BE                                                                      | 176 |

| Harald Servat, Cecilia González-Alvarez, Xavier Aguilar,                                               |     |

| Daniel Cabrera-Benitez, and Daniel Jiménez-González                                                    |     |

# IV Power-Aware Techniques

| COFFEE: COmpiler Framework for Energy-Aware Exploration<br>Praveen Raghavan, Andy Lambrechts, Javed Absar, Murali Jayapala,<br>Francky Catthoor, and Diederik Verkest | 193 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Integrated CPU Cache Power Management in Multiple Clock Domain<br>Processors                                                                                          | 209 |

| Variation-Aware Software Techniques for Cache Leakage Reduction<br>Using Value-Dependence of SRAM Leakage Due to Within-Die Process<br>Variation                      | 224 |

# V High-Performance Processors

| The Significance of Affectors and Affectees Correlations for Branch |     |

|---------------------------------------------------------------------|-----|

| Prediction                                                          | 243 |

| Yiannakis Sazeides, Andreas Moustakas,                              |     |

| Kypros Constantinides, and Marios Kleanthous                        |     |

| Turbo-ROB: A Low Cost Checkpoint/Restore Accelerator         Patrick Akl and Andreas Moshovos                                                           | 258 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| LPA: A First Approach to the Loop Processor Architecture<br>Alejandro García, Oliverio J. Santana, Enrique Fernández,<br>Pedro Medina, and Mateo Valero | 273 |

# VI Profiles: Collection and Analysis

| Complementing Missing and Inaccurate Profiling Using a Minimum<br>Cost Circulation Algorithm<br>Roy Levin, Ilan Newman, and Gadi Haber         |     |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Using Dynamic Binary Instrumentation to Generate Multi-platform<br>SimPoints: Methodology and Accuracy<br>Vincent M. Weaver and Sally A. McKee | 305 |  |  |  |

| Phase Complexity Surfaces: Characterizing Time-Varying Program<br>Behavior<br>Frederik Vandeputte and Lieven Eeckhout                          | 320 |  |  |  |

| VII Optimizing Memory Performance                                                                                                              |     |  |  |  |

| MLP-Aware Dynamic Cache Partitioning<br>Miquel Moreto, Francisco J. Cazorla, Alex Ramirez, and<br>Mateo Valero                                 | 337 |  |  |  |

| Compiler Techniques for Reducing Data Cache Miss Rate on a                                                                                     |     |  |  |  |

| Multithreaded Architecture<br>Subhradyuti Sarkar and Dean M. Tullsen                                                                           | 353 |  |  |  |

| Chun-Chieh Lin and Chuen-Liang Chen                                                 |     |

|-------------------------------------------------------------------------------------|-----|

| Aggressive Function Inlining: Preventing Loop Blockings in the<br>Instruction Cache | 384 |

| Author | Index | <br> | <br> | <br> | <br>399 |

|--------|-------|------|------|------|---------|

|        |       |      |      |      |         |

**Invited Program**

# Supercomputing for the Future, Supercomputing from the Past (Keynote)

Mateo Valero and Jesús Labarta

Barcelona Supercomputing Center and Universitat Politcnica de Catalunya, Barcelona

**Abstract.** Supercomputing is a zero billion dollar market but a huge driving boost for technology and systems for the future.

Today, applications in the engineering and scientific world are the major users of the huge computational power offered by supercomputers. In the future, the commercial and business applications will increasingly have such high computational demands.

Supercomputers, once built on technology developed from scratch have now evolved towards the integration of commodity components. Designers of high end systems for the future have to closely monitor the evolution of mass market developments. Such trends also imply that supercomputers themselves provide requirements for the performance and design of those components.

The current technology integration capability is actually allowing for the use of supercomputing technologies within a single chip that will be used in all markets. Stressing the high end systems design will thus help develop ideas and techniques that will spread everywhere. A general observation about supercomputers in the past is their relatively static operation (job allocation, interconnect routing, domain decompositions, loop scheduling) and often little coordination between levels.

Flexibility and dynamicity are some key ideas that will have to be further stressed in the design of future supercomputers. The ability to accept and deal with variance (rather than stubbornly trying to eliminate it) will be important. Such variance may arise from the actual manufacturing/operation mode of the different components (chip layout, MPI internals, contention for shared resources such as memory or interconnect, ...) or the expectedly more and more dynamic nature of the applications themselves. Such variability will be perceived as load imbalance by an actual run. Properly addressing this issue will be very important.

The application behavior typically shows repetitive patterns of resource usage. Even if such patterns may be dynamic, very often the timescales of such variability allows for the application of prediction techniques and matching resources to actual demands. Our foreseen systems will thus have dynamic mechanisms to support fine grain load balancing, while the policies will be applied at a coarse granularity.

As we approach fundamental limits in single processor design specially in terms of the performance/power ratio, multicore chips and massive parallelism will become necessary to achieve the required performance levels. A hierarchical structure is one of the unavoidable approaches to future systems design. Hierarchies will show up at all levels from processor to node and system design, both in the hardware and in the software.

The development of programming models (extending current ones or developing new ones) faces a challenge of providing the mechanism to express a certain level of hierarchy (but not too much/detailed) that can be matched by compilers, run times and OSs to the potentially very different underlying architectures. Programmability and portability of the programs (both functional and performance wise, both forward and backwards) is a key challenge for these systems.

The approach to address a massively parallel and hierarchical system with load balancing issues will require coordination between different scheduling/resource allocation policies and a tight integration of the design of the components at all levels: processor, interconnect, run time, programming model, applications, OS scheduler, storage and Job scheduler.

By approaching the way of operation between supercomputers and general purpose, this zero billion dollar market can play a very important role of future unified-computing.

#### **Biography of Mateo Valero**

Mateo Valero obtained his PhD at UPC in 1980. He is a professor in the Computer Architecture Department at UPC. His research interests focus on high performance architectures. He has published approximately 400 papers on these topics. He is the director of the Barcelona Supercomputing Center, the National Center of Supercomputing in Spain. Dr. Valero has been honored with several awards. Among them, the Eckert-Mauchly Award in 2007, by the IEEE, Institute of Electrical and Electronics Engineers and the ACM, the Association for Computing Machinery, the King Jaime I in research by the Generalitat Valenciana in 1997 presented by the Queen of Spain, and two Spanish National awards, the Julio Rey Pastor in 2001, to recognize research on IT technologies, and the Leonardo Torres Quevedo in 2006, to recognize research in Engineering, by the Spanish Ministery of Science and Technology, presented by the King of Spain.

In December 1994, Professor Valero became a founding member of the Royal Spanish Academy of Engineering. In 2005 he was elected Correspondant Academic of the Spanish Royal Academy of Science and in 2006, member of the Royal Spanish Academy of Doctors. In 2000 he became a Fellow of the IEEE. In 2002, he became an Intel Distinguished Research Fellow and a Fellow of the ACM, the Association for Computing Machinery. In 1998 he won a Favourite Son Award of his home town, Alfamn (Zaragoza) and in 2006, his native town of Alfamn named their Public College after him.

#### **Biography of Jess Labarta**

Jess Labarta is full professor on Computer Architecture at the Technical University of Catalonia (UPC) since 1990. Since 1981 he has been lecturing on computer architecture, operating systems, computer networks and performance evaluation. His research interest has been centered on parallel computing, covering areas from multiprocessor architecture, memory hierarchy, parallelizing compilers, operating systems, parallelization of numerical kernels, performance analysis and prediction tools.

Since 1995 till 2004 he was director of CEPBA (European Center of Parallelism of Barcelona) where he has been highly motivated by the promotion of parallel computing into industrial practice, and especially within SMEs. Since 2000 he has been strongly committed in carrying out and promoting productive research cooperation with IBM as part of the CEPBA-IBM Research Institute. Since 2005 he is responsible of the parallel computing research team within the Barcelona Supercomputing Center (BSC).

His major directions of current work relate to performance analysis tools, programming models (OpenMP for SMPs and clusters, CellSuperscalar for the Cell processor and Grid Superscalar for distributed environments) and resource management. His team distributes the CEPBA tools (Paraver and Dimemas).

# Part I

# Multithreaded and Multicore Processors

# MIPS MT: A Multithreaded RISC Architecture for Embedded Real-Time Processing

Kevin D. Kissell

MIPS Technologies Inc. 39 chemin des Martelles, 06620 Le Bar sur Loup, France Tel.: +33 4.93.42.45.15; Fax: +33 4.93.42.45.13. kevink@acm.org http://www.mips.com/

**Abstract.** The MIPS® MT architecture is a fine-grained multithreading extension to the general-purpose MIPS RISC architecture. In addition to the classical multithreaded provision for explicit exploitation of cuncurrency as a mechanism for latency tolerance, MIPS MT has unique features to address the problems of real-time and embedded computing in System-on-a-Chip environments. This paper provides an overview of the MIPS MT architecture and how it can variously be exploited to improve computational bandwidth, real time quality of service, and response time to asynchronous events.

# 1 Multithreading and Embedded Processors

Most of the work that has been done in multithreaded processor architecture over the years [1] has been motivated by the demands of high-performance on computational workloads. However, from the very beginning, starting with the multithreaded peripheral processor of the CDC 6600 [2], multithreading has been recognized as a valuable architectural tool for real-time and embedded processing. In recent years, specialized multithreaded processor architectures for network data-plane processing have been proposed and deployed with some success [3][4], but their adoption has been limited because of the non-standard instruction sets, software tools, and environments.

In late 2002, the author's group at MIPS Technologies Inc. began the investigation of the extension of the standard MIPS32® RISC architecture to encompass explicit multithreading as a superset extension. The resulting multithreading architecture, MIPS MT, has been instantiated in a synthesizable processor, the MIPS32 34K<sup>TM</sup> core, which has served as a platform for verification and research.

The development of the MIPS MT architecture was constrained by a set of philosophical principles:

- 1. *Scalability*. The architecture must be implementable and useful on processor implementations spanning orders of magnitude in size and complexity, from micro-controllers to numerical supercomputer nodes.

- 2. *Run-time Efficiency*. Basic operations of thread creation and destruction, and of inter-thread communication and synchronization, must be realizable in a minimal number of clock cycles, and without OS intervention in the most probable cases.

© Springer-Verlag Berlin Heidelberg 2008

- 3. *Virtualizability.* The physical resources which support multithreading must be invisible or abstracted to user-mode software, such that an application which consumes more resources than are physically implemented on a given MIPS MT platform can nevertheless execute correctly, given appropriate OS support.

- 4. *Migratability*. The architecture must allow threads to migrate from processor to processor to balance load, and be amenable to multithreaded/multi-core implementations.

- 5. *Scheduling Agnosticism*. The architecture must allow for a broad variety of thread scheduling models, while isolating these models from user-mode software.

# 2 The Hierarchy of Multithreaded Entities

MIPS MT defines two levels of multithreading, the VPE (Virtual Processing Element), which is a virtual processor implementing the full MIPS instruction set and privileged resource architecture, and the TC (for Thread Context), which is a lighter-weight "microthread" entity. This was largely dictated by the fact that the MIPS privileged resource architecture provides direct software access to a TLB and other resources that are relatively expensive to instantiate in a small design. However, it also provides a rich framework for dynamic multithreading under software control. A VPE can have a variable number of TCs bound to it, sharing its privileged resources.

# 2.1 VPEs as Exception Domains

A MIPS MT VPE can be thought of as an exception domain. A single MMU and a single set of system coprocessor registers for exception management exists per VPE, shared by as many TC microthreads as may be bound to the VPE. There is, for example, a single exception program counter register to indicate where execution should be resumed at the end of exception service. It thus becomes essential that, when an exception is dispatched, thread scheduling within the VPE be suspended until software can sample the relevant privileged resource state and acknowledge the exception. In the base MIPS architecture, the exception entry state is already indicated by a privileged resource architecture state bit (EXL), which is cleared automatically on a return from exception. In MIPS MT, that bit is instantiated per-VPE, and acts as an inhibitor of multithreaded issue.

Synchronous exceptions, such as TLB and floating-point exceptions, are serviced by the microthread which caused them. Asynchronous interrupt exceptions, however, are asserted at the VPE level and serviced opportunistically by any available TC bound to the VPE. A TC can be excluded from the interrupt service pool of its associated VPE by setting a per-TC "interrupt exemption" bit. While only one interrupt exception may be dispatched at a time in a VPE, once the critical state has been captured by the exception vector, interrupts can be re-enabled, allowing multiple interrupt service routines to execute concurrently within a VPE.

#### 2.2 VPEs as Scheduling Domains

Privileged software can atomically enable and disable multithreaded execution within a VPE without directly affecting other VPEs of the same processor core. The MIPS MT architecture is scheduling-agnostic, but defines a software interface to the implementation-specific hardware thread scheduling logic. This interface is implemented hierarchically, at both the level of the VPE and the level of the TC. This is discussed further in section 5.

#### **3** Thread Creation and Destruction

One of the design objectives of MIPS MT was to allow for lightweight creation and destruction of concurrent threads of execution, since the overhead of thread creation and destruction can create a lower bound on the granularity of parallelism that can be exploited. In MIPS MT, a microthread can be created and assigned to a TC using the FORK instruction, and conditionally terminated using the YIELD instruction.

#### 3.1 Thread Creation with FORK

The MIPS MT FORK instruction causes a new microthread to begin execution, provided that the hardware resources are available to do so. While other architectures have proposed fork instructions with semantics similar to that of the traditional UNIX *fork()* system call, where the operation replicates the full software-visible state of the thread context [5], the MIPS MT FORK instruction follows the basic rules of the MIPS RISC instruction set: It requires no more than 2 general-purpose register reads and 1 GPR write, so that it can be fully pipelined in a straightforward design. A starting instruction fetch address and an arbitrary register value are read from the FORKing thread's registers, and the arbitrary value is written to the specified register of the FORKed TC. If more than a single register value needs to be transmitted to the new microthread, the necessary values are passed via memory - in most cases the primary data cache.

Unlike dynamic thread creation in the Tera MTA[6][7], which is a two-phase process involving RESERVE and CREATE operations to allocate and, if the allocation was successful, launch a new thread, the MIPS MT FORK is "optimistic". Either a dynamically allocatable TC is free to be FORKed, and the operation succeeds, or the FORK instruction throws a *thread overflow* exception to be caught by the operating system. The OS can then determine whether to swap out some TCs state and make it available to the restarted FORK, to emulate the operation by creating a new OS-level thread to time-share in the system, or to signal an error. FORK is thus "virtualizable".

It is worth noting that a successful FORK provides no "handle" to the FORKing thread by which it might reference the thread it created. In part, this is due to the GPR write port rule alluded to above, but there is also a philosophical argument. While it would be trivial to provide an ephemerally valid value, such as the index into the physical array of TCs, the software thread created might be interrupted, swapped out, or migrated at any time. A persistent hardware handle that would follow a software thread for its entire lifetime would be of some utility, but the complexity associated with creating and maintaining such a handle does not seem to be warranted in an architecture that needs to scale down to microcontroller-class implementations.

#### 3.2 Thread Termination with YIELD

The YIELD instruction serves several purposes in MIPS MT. Some of these will be described below in section 5, but one important one is that of terminating a dynamically allocated thread. If the input argument to YIELD is zero, the TC associated with the instruction stream changes state from being active to being "free", and available for use by a subsequent FORK.

If the last active TC within a VPE executes a YIELD \$0 instruction, so that all execution would stop on the VPE, a *thread underflow* condition exists, and an exception is taken. It is up to the operating system to determine the correct action to take.

# 4 Inter-thread Synchronization

The efficiency of inter-thread synchronization is another key factor that limits the granularity of concurrency that can be exploited by a multithreaded architecture. The standard synchronization mechanism in the MIPS architecture is the load-linked/store-conditional operator pair. This mechanism must work on MIPS MT processors, for compatibility, but spin-lock semantics are highly undesirable on a multithreaded processor. The act of spinning and retrying a lock consumes issue and memory bandwidth that would better be used by the thread holding it, to make progress towards its release.

While the power and generality of extending memory load/store semantics with the notion of empty/full synchronization has been demonstrated in systems like the Denelcor HEP[8], the Tera MTA and the Alewife machine[9], the simplicity of the concept belies the costs of implementation. Designers of cost-sensitive embedded systems-onchips are not willing to pay the price to provide a main memory with empty/full attributes.

Rather than require empty/full support for all of memory, the MIPS MT architecture defines the notion of *gating storage*, which is some subset of the physical address space which has the property that loads and stores to it can block for unbounded periods of time, and can be aborted and restarted without any side-effects. A specific variety of gating storage defined by MIPS MT is the "ITC" (Inter-thread Communication) store. The ITC store is broken up into *cells*, each of which has a set of *views*, which are distinguished by low-order address bits. To software, an ITC cell looks like a data structure in memory, but instead of having distinct and independent data in each element of the data structure, loads and stores to different elements of a cell operate on the same data, but with different semantics. A C language description might be:

```

typedef volatile long long viewtype;

typedef struct {

viewtype bypass; /* Non-blocking read/write */

viewtype control; /* Exposes Empty/Full state, etc. */

viewtype ef_sync; /* Empty/Full blocking load/store */

```

```

viewtype ef_try; /* Empty/Full non-blocking poll */

viewtype pv_sync; /* PV Semaphore blocking load/store */

viewtype pv_try; /* PV Semaphore non-blocking poll */

viewtype reserved[10]; /* Reserved for future views */

} itc_cell;

```

For example, the *ef\_sync* cell view provides classical blocking empty/full semantics, such that if itc\_ptr is a pointer to an *itc\_cell* in an "empty" state, then

```

x = itc_ptr->ef_sync;

```

will cause the executing thread to be suspended until such time as some other instruction stream performs an operation like

```

itc_ptr->ef_sync = y;

```

at which point the first thread's *x* variable will pick up the value of *y*, and it will resume execution.

The  $pv\_sync$  view provides a more complex primitive, that of a counting, or PV semaphore[10]. Stores which reference this view cause the value of the cell to be atomically incremented, regardless of the register value stored, while loads return the value and perform a post-decrement if it is non-zero. If the pre-load value is zero, the load blocks until a  $pv\_sync$  store is done.

The "try" views allow for non-blocking synchronization, using either the empty/full or the P/V paradigm. In the  $pv\_try$  case, loads return the cell data value, even if zero, performing an auto-decrement only if the pre-load value was non-zero. In the  $ef\_try$ case, loads references return zero if the cell is empty, regardless of the last data value written, and stores may be attempted using the MIPS32 SC (store conditional) instruction, which will indicate failure if the cell is full. Whereas the  $ef\_sync$  view allows arbitrary data to be passed through the cell, the use of a zero value to indicate the failure of a load from an  $ef\_try$  view implies that a word value of zero cannot be passed. In the most frequent use case, however, it is pointers that are passed between threads via the ITC cell, and a null pointers and non-pointers from an empty cell can be treated alike.

# 5 Hybrid Scheduling Control

Most of the study and application of multithreaded processor architecture has focused on multithreading as a latency tolerance technique, a means of keeping fast functional units busy in the face of long operand delays. This is of value in computationally intensive embedded applications, but in many cases, it is the ability to provide latency *avoidance*, rather than latency tolerance, where multithreading provides an advantage in such systems[11]. MIPS MT provides architectural support for this in several ways, allowing processor hardware, system and application software, and external logic to jointly control the scheduling of instruction streams.

#### 5.1 Zero-Latency Event Service Using YIELD Instructions

The use of the YIELD instruction for thread termination was described in section 3.2 above, but the YIELD instruction is in fact a general tool for controlling the execution

of a thread. A processor implementing MIPS MT has up to 31 yield qualifier inputs, to be connected to indicators of events external to the core. When a YIELD instruction is issued with a positive input operand value, that value is interpreted as a vector of orthogonal bits corresponding to the yield qualifier inputs. If none of the qualifier inputs corresponding to the operand value are asserted, execution of the thread is suspended until such time as one of them goes active.

The ability to suspend execution based on a particular yield qualifier can be controlled by the operating system, using a privileged mask register. If a program issues a YIELD where the input value has a set bit that is not set in the mask register, an exception is delivered on the YIELD. This allows operating systems to prevent unauthorized programs using input state as a covert channel, and allows virtualization, whereby a program executing on a VPE to which a particular yield qualifier input is not connected can have the YIELD operation emulated by the OS, in response to the illegal qualifier exception.

Event service gated by YIELD instructions has potentially less latency than interrupts, even those handled by dedicated interrupt threads or shadow register files, because in addition to eliminating the need to save and restore context, there is no control transfer to a vector, which would typically require a pipeline flush, and no decode of state to determine where to resume event processing. In the case of the 34K-family cores, which have a per-TC instruction buffer (IB), the instruction following the YIELD is generally already in the IB, ready to issue once the YIELD ceases to be blocked.

#### 5.2 Hierarchically Programmable Scheduling

In MIPS MT, each VPE and each TC has two registers of privileged resource state associated with its scheduling; a control register and a feedback register. The scheduling control registers allow software to express dynamic information, such as priority or a TDMA schedule, to a hardware scheduling policy manager, while the scheduling feedback registers allow the scheduling hardware to provide feedback, such as the number of instructions issued or retired by the VPE or TC.

The 34K processor core design features a modular scheduling policy manager that can be replaced or modified to suit the quality-of-service requirements of a particular application.

#### 5.3 Gating Storage as a Peripheral Interface

In addition to its primary function of providing inter-thread synchronization for software, I/O FIFOs can be mapped into the gating storage space, so that threads can be programmed to consume or produce data in an open loop. Their execution will then be governed by the ability of the peripherals connected to the FIFOs to consume or produce data.

# 6 Virtualization of MIPS MT Resources

In order to better support the portability of applications across different MIPS MT implementations, the new user-visible resources defined by the architecture: FORKed threads, ITC cells, and YIELD qualifiers, are all virtualizable.

#### 6.1 Thread Context Virtualization

User-mode code has no knowledge of which physical TC it is using, nor which physical TC is allocated by a successful FORK instruction. All interaction between concurrently executing threads is done via shared memory or memory-like storage, and there is no architectural assumption made about whether it is the "parent" or "child" which executes first after a FORK.

When a FORK instruction is issued, it is transparent to the application whether a TC was allocated and launched, or whether a thread overflow exception was taken instead. In response to the thread overflow exception, an operating system has the option of treating it as a fatal application error, treating it as an exception to be raised to the application, or emulating the operation.

Emulation of a FORK implies hybrid scheduling, wherein the multithreaded processor schedules among the threads resident in N TCs, while system software multiplexes M>N software threads across those N TCs. The MIPS MT architecture facilitates this with MFTR (Move From Thread Register) and MTTR (Move To Thread Register) instructions, which allow a privileged thread running on one TC to halt another TC and manipulate its contents, and with the per-TC scheduling feedback registers that allow the forward progress of each thread to be monitored.

TCs which are blocked on ITC references or YIELD instructions may be halted and swapped-out without any side-effect on the software-visible state of the thread or of the ITC storage.

#### 6.2 ITC Storage Virtualization

ITC storage is a special case of physical memory, and can be mapped and protected by the MIPS32 MMU. Unlike physical memory, ITC storage cannot be swapped in or out with direct I/O operations. System software must extract and restore both the cell data and the cell control state, via the bypass and control views, respectively.

#### 6.3 **YIELD Qualifier Virtualization**

The MIPS MT architecture exposes a new set of physical inputs, the YIELD qualifiers, to user-mode software. To allow for trap and emulation of qualified YIELD operations, each VPE has a privileged mask register to selectively enable the YIELD qualifiers. If an application's YIELD instruction attempts to wait on an input that has not been enabled in the associated mask, an exception is taken. The operating system can then implement an appropriate policy of termination, raising of a software exception, or emulation of the YIELD with a software suspension of the thread.

#### 7 Software Use Models

The flexibility of the MIPS MT architecture as a multithreading framework has been demonstrated in the development of four different operating system models. All of them proved usable, and each has its distinct advantages.

# 7.1 Asymmetric Multiple Virtual Processors (AMVP)

In this model, different operating systems execute on different VPEs of the same processor core. Typically, this consists of a feature-rich multi-tasking OS such a Linux on one VPE and a low-level real-time OS on the other(s). Such a configuration exploits the independence of the VPE scheduling domains and allows a single processor core to handle a mix of hard-real-time and high-level user interface functions that would normally require multiple processors.

# 7.2 Symmetric Multiple Virtual Processors (SMVP)

As each VPE of a MIPS MT processor implements the full MIPS privileged resource architecture, it is trivial to adapt an SMP operating system to treat each VPE as a CPU. The level of concurrency available to applications is limited to the number of VPEs. In the case of a single-core system, if caches are common to all VPEs, interprocessor cache coherence support can be optimized out.

# 7.3 Symmetric Multiple TC (SMTC)

An SMTC OS extends SMP processor management to the TC level, so that a MIPS MT TC appears to the user to be a full CPU in an SMP system, allowing a higher degree of concurrency to be exploited. Since TCs do not implement the full privileged resource architecture, some features must be emulated by the OS, at some cost in complexity and performance.

# 7.4 The ROPE Kernel

The ROPE kernel is an experimental Linux kernel for MIPS MT processors. Rather than being based on an SMP configuration, the ROPE kernel is a uniprocessor kernel in which each kernel "thread" is itself potentially multithreaded. Each context switch saves the state of all active TCs of the kernel thread being switched-out, and restores the state of as many active TCs as were saved for the kernel thread being switched-in. On a trap or system call, multi-threaded issue is suspended until user-mode execution is resumed. The fact that the kernel model is single-threaded is thus not a problem.

Whereas the SMVP and SMTC kernels activate at boot time all TCs that are to be used by Linux processes, the ROPE kernel allows for dynamic thread creation/destruction without OS intervention, using the FORK and YIELD instructions. If more FORKs are performed than there are allocatable TCs, a Linux signal is sent to the FORKing process. While SMVP and SMTC OS models allow thread-level concurrency between unrelated threads and processes, and for both application and OS execution, the ROPE kernel supports only application-level concurrency, and only in explicitly multithreaded programs.

Source code for AMVP, SMVP, and SMTC Linux kernels for the 34K processor has been accepted by the kernel maintainers and is available from the source repositories at www.linux-mips.org and www.kernel.org.

# 8 Experimental Results

The following are experimental results obtained on an FPGA implementation of the 34K processor with 5TCs, running on the MIPS Malta<sup>™</sup> development board, using the ROPEbench framework developed by Jacob Leverich of Stanford. Each benchmark is run for a constant large number of iterations, divided among some number of software threads. The results are the calculated cycles-per-iteration.

On a uniprocessor configuration, each software thread is a *pthread*, time-sharing a single virtual CPU. In the SMTC configurations, each pthread represents a kernel thread scheduled according to standard SMP algorithms across 5 virtual CPUs. In the ROPE configuration, each pthread represents a ROPE microthread, of which the kernel has no direct knowledge. The uniprocessor and "SMTC-PT" systems use the pthread mutex implementation of the Linux glibc 2.4. The "SMTC-ITC" and ROPE systems use an experimental library using MIPS MT ITC cells mapped into the program's address space.

#### 8.1 Synchronization

The "Ferris wheel" benchmark measures synchronization costs between threads, where N threads are organized as a logical ring, each repeatedly acquiring a lock that must first be released by its predecessor. It's inner loop is:

```

for (i = 0; i < count; i++) {

lock(wheel, me);

unlock(wheel, next);

}</pre>

```

| Cycles/<br>Iteration | 1 Thread | 2 Threads | 3 Threads | 4 Threads | 5 Threads |

|----------------------|----------|-----------|-----------|-----------|-----------|

| Uniprocessor         | 414      | 2046      | 2494      | 2792      | 3004      |

| SMTC-PT              | 572      | 2052      | 11833     | 13556     | 14451     |

| SMTC-ITC             | 27       | 19        | 19        | 19        | 19        |

| ROPE                 | 26       | 18        | 18        | 18        | 18        |

| Table 1. Ferris Wh |

|--------------------|

|--------------------|

There are two noteworthy phenomena here. One is that the classical software pthread implementation degrades significantly as SMP threads are added. In the uniprocessor case, it is only by a rare accident of pre-emption that there will be contention for a low-level lock, but with multiple concurrent instruction streams active, such contention becomes increasingly likely.

The second phenomenon worth noting is that using the MIPS MT ITC store to implement the mutex in hardware is more than an order of magnitude faster, and does not suffer from the same scaling problems.

#### 8.2 Thread Creation/Destruction

The "Split/Join" benchmark creates threads which promptly exit, and synchronizes with their termination. The inner loop looks like:

```

for (i = 0; i < count; i++) {

thread_t th;

thread_create(&th, slave, NULL);

thread_join(th);

}</pre>

```

| Cycles/<br>Iteration | 1 Thread | 2 Threads | 3 Threads | 4 Threads | 5 Threads |

|----------------------|----------|-----------|-----------|-----------|-----------|

| Uniprocessor         | 34990    | 31790     | 31361     | 33042     | 33070     |

| SMTC-PT              | 38193    | 29978     | 29736     | 30276     | 29730     |

| SMTC-ITC             | 39150    | 31125     | 29473     | 29450     | 30660     |

| ROPE                 | 583      | 404       | -         | -         | -         |

Table 2. Split/Join

Note that the inner loop is itself executed concurrently by each of the test threads, so the maximum number of threads executing is twice the number of test threads. As the 34K test platform was equipped with only 5 TCs, the ROPE kernel could not support more than 2 test threads. As noted in section 3.1, failing FORK instructions can be trapped and emulated by an OS, but this was not implemented in the ROPE kernel prototype.

Within the limitations of hardware, however, the ROPE runtime's use of the MIPS MT FORK instruction is at least 60 times as efficient, at the system level, as the standard pthread library and SMP OS.

#### 8.3 Latency Tolerance

The type and degree of latency tolerance that can be realized with a MIPS MT processor is very much a function of the microarchitecture of the particular processor. The MIPS32 34K has a relatively simple single-issue, in-order pipeline, but can switch threads on a cycle-by-cycle basis to fill memory and functional unit stalls.

#### 8.3.1 Memory Latency

The effectiveness of multithreading in tolerating memory latency can be observed in comparing the results of two memory benchmarks, one of which issues load every 8 instructions which hits in the cache, the other of which differs only in that the address calculation always results in a cache miss.

| Cycles/<br>Iteration | 1 Thread | 2 Threads | 3 Threads | 4 Threads | 5 Threads |

|----------------------|----------|-----------|-----------|-----------|-----------|

| Uniprocessor         | 9.1      | 9.0       | 9.1       | 9.1       | 9.0       |

| SMTC-PT              | 9.6      | 8.5       | 8.4       | 8.2       | 8.2       |

| SMTC-ITC             | 9.7      | 8.5       | 8.4       | 8.2       | 8.2       |

| ROPE                 | 9.1      | 8.0       | 8.1       | 8.0       | 8.1       |

Table 3. Load Cache Hit

Table 4. Load Cache Miss

| Cycles/<br>Iteration | 1 Thread | 2 Threads | 3 Threads | 4 Threads | 5 Threads |

|----------------------|----------|-----------|-----------|-----------|-----------|

| Uniprocessor         | 95       | 95        | 95        | 95        | 95        |

| SMTC-PT              | 99       | 54        | 42        | 37        | 35        |

| SMTC-ITC             | 88       | 53        | 43        | 37        | 35        |

| ROPE                 | 83       | 51        | 41        | 37        | 34        |

The interleaving of execution with load stall time more than doubles the throughput of this particular test, so long as 3 or more TCs are active.

Memory latency affects not only data references, but also instruction fetches. The 34K processor core fills stall cycles due to instruction cache misses, provided that there are instructions in some other IB that can be issued. But if the processor is experiencing a large number of instruction cache misses, by definition, the number of available instructions in the IBs is reduced, limiting the opportunity for multithreaded issue.

The experiment for measuring the effects of multithreading on instruction cache miss-intensive code consists of a set of linear instruction sequences, one for each thread, each larger than the instruction cache of the processor. Each sequence consists of a series of 5000 jumps forward to the next cache line. As the 34K processor's cache line size is four words, the sequence looks like the following.

```

labelN:

j labelNplus1

nop

nop

labelNplus1:

j labelNplus2

```

| Cycles/Jump  | 1 Thread | 2 Threads | 3 Threads | 4 Threads | 5 Threads |

|--------------|----------|-----------|-----------|-----------|-----------|

| Uniprocessor | 45       | 45        | 45        | 45        | 45        |

| SMTC-PT      | 48       | 31        | 31        | 34        | 37        |

| SMTC-ITC     | 48       | 31        | 30        | 34        | 38        |

| ROPE         | 45       | 30        | 30        | 34        | 38        |

Table 5. Instruction Cache Miss

The 34K processor implementation used in this experiment has only two memory transaction buffers for instruction cache fills, with pre-arbitration and reservation of a buffer for the first thread to be stalled on the instruction fill resource. The experimental data reflects these implementation details: Runs with two and three threads show some significant overlap of fetch miss stalls, but adding more threads beyond the first 3 adds additional resource contention without any corresponding increase in hardware concurrency.

#### 8.3.2 Functional Unit Latency

The 34K microarchitecture also exploits scheduling opportunities created by functional unit stalls for operations with more than a single-cycle latency. The following loop compiles to 7 instructions, 5 of which are targeted multiplies.

```

for (i = 0; i < count; i++) {

r1 *= 239875981;

r2 *= r1;

r3 *= r2;

r4 *= r3;

r5 *= r4;

}</pre>

```

| Table 6. | Integer | Multiplication |

|----------|---------|----------------|

|----------|---------|----------------|

| Cycles/<br>Iteration | 1 Thread | 2 Threads | 3 Threads | 4 Threads | 5 Threads |

|----------------------|----------|-----------|-----------|-----------|-----------|

| Uniprocessor         | 21       | 21        | 21        | 21        | 21        |

| SMTC-PT              | 22       | 14        | 11        | 9         | 8         |

| SMTC-ITC             | 22       | 14        | 11        | 9         | 8         |

| ROPE                 | 21       | 13        | 10        | 9         | 8         |

As was the case with the cache miss benchmark, the effective multiply throughput is more than doubled when 3 or more threads are used.

# 9 Conclusions

The MIPS MT architecture represents another case of supercomputer architecture techniques of the 20th century finding application in the embedded systems of the 21st century. The effectiveness of multithreading for latency tolerance is demonstrable in small-scale systems. The effectiveness of multithreading for latency avoidance, given the architectural support of MIPS MT, is less hostage to other system design parameters, and at least as relevant to practical application in real-time and embedded domains.

# References

- Ungerer, T., et al.: A Survey of Processors with Explicit Multithreading. ACM Computing Surveys 35(1), 29–63 (2003)

- [2] Thornton, J.E.: Design of a Computer: The CDC 6600. Foresman and Company, Scott (1970)

- [3] El-Haj-Mahmoud, Rotenberg: Safely Exploiting Multithreaded Processors to Tolerate Memory Latency in Real-Time Systems. In: Proceedings of CASES 2004, pp. 2-13 (2004)

- [4] Ubicom, Inc. The Ubicom IP3023 Wireless Network Processor (2003), Available from http://www.ubicom.com/pdfs/whitepapers/WP-IP3023WNP-01.pdf

- [5] Papadopoulos, Traub: Multithreading: A Revisionist View of Dataflow Architectures. In: Proceedings of ISCA 1991, pp. 342–351 (1991)

- [6] Alverson, G., et al.: The Tera Computer System. In: Proceedings of the 1990 International Conference on Supercomputing, Amsterdam, The Netherlands, pp. 1–6 (1990)

- [7] Alverson, G., et al.: Exploiting Heterogeneous Parallelism on a Multithreaded Multiprocessor. In: Proceedings of the 6th International Conference on Supercomputing, pp. 188–197 (1992)

- [8] Hwang, Briggs: Computer Architecture and Parallel Processing, pp. 679–680. McGraw Hill, New York (1984)

- [9] Agarwal, A., et al.: The MIT Alewife Machine: Architecture and Performance. In: Proceedings of ISCA 1995, pp. 2–13 (1995)

- [10] Dijkstra, E.W.: Cooperating Sequential Processes. In: Genuys, F. (ed.) Programming Languages, pp. 43–112 (1968)

- [11] Hoover, G., et al.: A Case Study of Multi-Threading in the Embedded Space. In: Proceedings of the 2006 International Conference on Compilers, Architecture, and Synthesis for Embedded Systems, pp. 357–367 (2006)

# rMPI: Message Passing on Multicore Processors with On-Chip Interconnect

James Psota and Anant Agarwal

Massachusetts Institute of Technology, Cambridge, MA 02139, USA

Abstract. With multicore processors becoming the standard architecture, programmers are faced with the challenge of developing applications that capitalize on multicore's advantages. This paper presents rMPI, which leverages the onchip networks of multicore processors to build a powerful abstraction with which many programmers are familiar: the MPI programming interface. To our knowledge, rMPI is the first MPI implementation for multicore processors that have on-chip networks. This study uses the MIT Raw processor as an experimentation and validation vehicle, although the findings presented are applicable to multicore processors with on-chip networks in general. Likewise, this study uses the MPI API as a general interface which allows parallel tasks to communicate, but the results shown in this paper are generally applicable to message passing communication. Overall, rMPI's design constitutes the marriage of message passing communication and on-chip networks, allowing programmers to employ a wellunderstood programming model to a high performance multicore processor architecture.

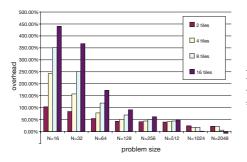

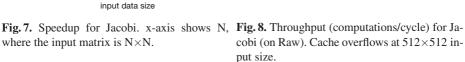

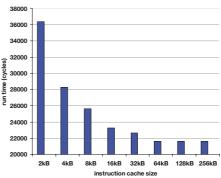

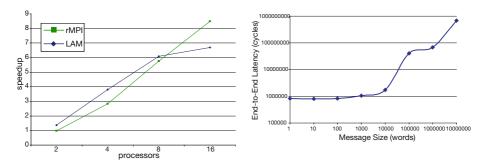

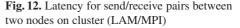

This work assesses the applicability of the MPI API to multicore processors with on-chip interconnect, and carefully analyzes overheads associated with common MPI operations. This paper contrasts MPI to lower-overhead network interface abstractions that the on-chip networks provide. The evaluation also compares rMPI to hand-coded applications running directly on one of the processor's low-level on-chip networks, as well as to a commercial-quality MPI implementation running on a cluster of Ethernet-connected workstations. Results show speedups of 4x to 15x for 16 processor cores relative to one core, depending on the application, which equal or exceed performance scalability of the MPI cluster system. However, this paper ultimately argues that while MPI offers reasonable performance on multicores when, for instance, legacy applications must be run, its large overheads squander the multicore opportunity. Performance of multicores could be significantly improved by replacing MPI with a lighter-weight communications API with a smaller memory footprint.

# 1 Introduction

Next-generation microprocessors will increasingly rely on parallelism, as opposed to frequency scaling, for improvements in performance scalability. Microprocessor designers are attaining such parallelism by placing multiple processing cores on a single piece of silicon, a feat now achievable thanks to the technology scaling described by Moore's Law [2]. Most multicore processors such as the POWER5 and AMD Opteron 800 force interprocessor communication to go through the memory system, which can

be slow, but some offer first-class on-chip inter-core network support. Technology scaling is enabling such network-interconnected parallel systems to be built on a chip, offering users extremely low latency networks. The MIT Raw processor [33], [31], [30], [32] builds on this idea and provides a prototype to evaluate these ideas. Raw includes first-class instruction set architecture (ISA) support for inter-processor communication, enabling orders of magnitude improvement in communication latency.

This paper investigates the merits of tightly integrated on-chip networks, especially in light of their programmability and performance. This paper introduces rMPI, which provides a scalable interface that allows transparent migration of the large extant legacy code base which will have to run on multicores. rMPI leverages the on-chip network of the Raw multicore processor to build an abstraction with which many programmers are familiar: the Message Passing Interface (MPI). The processor cores that constitute chip multicores (CMPs) such as Raw are tightly coupled through fast integrated on-chip networks, making such CMPs quite different from more traditional heavily-decoupled parallel computer systems. Additionally, some CMPs eliminate many layers of abstraction between the user program and underlying hardware, allowing programmers to directly interact with hardware resources. Because of the removal of these layers, CMPs can have extremely fast interrupts with low overhead. Removing standard computer system layers such as the operating system both represents an opportunity for improved performance but also places an increased responsibility on the programmer to develop robust software. These and other novel features of multicore architectures motivated designing rMPI to best take advantage of the tightly-coupled networks and direct access to hardware resources that many CMPs offer. rMPI offers the following features: 1) robust, deadlock-free, and scalable programming mechanisms; 2) an interface that is compatible with current MPI software; 3) an easy interface for programmers already familiar with high-level message passing paradigms; 4) and fine-grain control over their programs when automatic parallelization tools do not yield sufficient performance.

Multicores with low-latency on-chip networks offer a great opportunity for performance and energy savings [29], [33]. However, this opportunity can be quickly squandered if programmers do not structure their applications and runtime systems in ways that leverage the aforementioned unique aspects of multicores. Multicores with onchip networks and small on-chip memories usually perform best when data are communicated directly from core to core *without accessing off-chip memory*, encouraging *communication-centric algorithms* [33]. Multcores also perform well when the underlying networks provide the ability to send fine-grain messages between cores within a few cycles. MPI was originally developed 15 years ago assuming coarser-grain communication between cores and communication overhead usually included operating system calls and sockets overhead. rMPI allows investigation into how well MPI, given its assumptions about system overheads, maps to multicore architectures with on-chip networks.

The evaluation of rMPI presented in this paper attempts to understand how well it succeeds in offering the above-mentioned features, and if MPI is still an appropriate API in the multicore domain. rMPI is evaluated in comparison to two references. To develop a qualitative intuition about the scaling properties of rMPI, it is compared against LAM/MPI, a highly optimized commercial MPI implementation running on a cluster of workstations. Additionally, it is compared against hand-coded and hand-orchestrated applications running on one of Raw's low-level on-chip dynamic networks on top of which rMPI was built. The comparison against the Raw network is an attempt to determine the overhead imposed by features that rMPI offers, which include the MPI programming interface, removal of sub-application-level deadlock potential, and automatic message packetization/reassembly. The sources of rMPI's overhead are determined by analyzing where cycles are spent in enacting both a send and a receive using MPI function calls for both short and long messages. Overall, we show that rMPI running on Raw can provide performance scalability that is comparable to a commercial MPI implementation running on a cluster of workstations by leveraging the underlying network architecture of the Raw processor. However, rMPI's overhead relative to the GDN varies from 5% to nearly 500%.

The rest of this paper is organized as follows. Section 2 provides an overview of the Raw architecture, focusing on the resources that are especially relevant to rMPI's design and operation. Section 3 discusses rMPI's design at a high level, and describes some of its optimizations. Section 4 provides detailed results. Section 5 discusses other work related to message passing on parallel computer systems. Finally, Section 6 concludes the paper.

# 2 Background

**RAW PROCESSOR.** Before investigating rMPI's design and implementation, a brief overview of the Raw processor must be given. The Raw processor consists of 16 identical tiles, which each contain a processing core and network components that allow for interprocessor communication. The processing cores each have an 8-stage in-order single-issue MIPS-style processing pipeline and a 4-stage single-precision pipelined FPU. The Raw chip also has four register-mapped on-chip networks which are exposed to the programmer through the Raw ISA. Additionally, tiles contain 32KB of hardware-managed data cache, 32KB of software-managed instruction cache, and 64KB of software-managed switch instruction memory. The Raw prototype was implemented in hardware with an ASIC process, and has been shown to perform well on a variety of application types [33].

Raw's software-exposed ISA allows programmers to directly control all of the chip's resources, including gates, wires, and pins. Programmers of Raw have the ability to carefully orchestrate data transfer between tiles simply by reading and writing registers. Raw has four 32-bit full-duplex on-chip networks, two static (routes specified at compile time) and two dynamic (routes specified dynamically at run time). rMPI leverages one of Raw's dynamic networks, the General Dynamic Network (GDN), for all communication between tiles prompted by an MPI communication routine.

rMPI relies on several key features of the GDN that necessitate elaboration. The GDN is a dimension-ordered wormhole routed network on which messages containing 32-bit header words are sent. In addition to containing routing information. The maximum GDN message size is 32 words, including the header, and the network guarantees that GDN messages arrive at the destination tile atomically and in-order. GDN messages from different senders sent to the same receiver may be interleaved and received

in a different order relative to the absolute time when each was sent. The GDN's atomicity constraint does guarantee, though, that the contents of individual GDN messages from different sources will not be interleaved with each other.

If the sending tile must communicate more than 32 words, it must break the message into pieces, which then must be re-assembled by the receiver. Managing many senders and many receivers in an all-to-all communication pattern clearly becomes challenging using the low-level GDN. Additionally, it is trivial to construct a communication pattern on the GDN which deadlocks the network—the GDN's input and output network ports are both blocking, and contain space for only four words and sixteen words of data, respectively. Thus, the programmer must construct programs which manage buffer space and communication patterns carefully to avoid deadlock. Raw also offers programmers fast interrupts that take less than 60 clock cycles of overhead for both call and return. This facility is exploited by rMPI to handle receiving messages from the network in an interrupt-driven manner.

**MPI.** In the parallel computing domain, MPI has become the *de-facto* standard for writing parallel applications. MPI is not an implementation or a language, but a standard with which implementations on different parallel computers must comply. Thus, programs written using MPI are portable: they can be moved from one parallel system to another, assuming both systems offer a valid MPI implementation. Overall, such portability is a key goal of MPI, providing a virtual computing model that hides many architectural details of the underlying parallel computer. MPI implementations exist for most high performance parallel computer systems, with LAM/MPI [6], [28] and MPICH [15], [34] being two of the most popular.

The MPI standard  $[\Pi 0]$ ,  $[\Omega]$  includes primitives for blocking and non-blocking pointto-point communications, collective operations (*e.g.*, broadcast, scatter and gather), process groups, communication topologies, and bindings for C, C++, and Fortran. The MPI standard is large, containing over 200 function calls. rMPI implements the blocking point-to-point communication routines (but not the non-blocking routines), collective operations, MPI datatypes, process groups, and communication topologies for C programs. More information about MPI is available in [27], [14], [26], [24].

# 3 Design

This section describes the design, architecture, and implementation of rMPI from a high level. rMPI is a runtime system that enables users to run MPI programs on Raw. rMPI leveraged many ideas from well-known open source MPI libraries, such as MPICH [34] and LAM/MPI [6], [28], but also attempted to implement the MPI standard in a way that leverages the unique resources that Raw provides. Indeed, multi-core processors with low-latency on-chip networks and fast interrupts serve as very different hardware platforms compared to a cluster of workstations interconnected via TCP/IP, and rMPI reflects these differences. rMPI consists of over 75,000 lines of code, written mostly in ANSI C. Much more detail on rMPI's implementation can be found in [25].

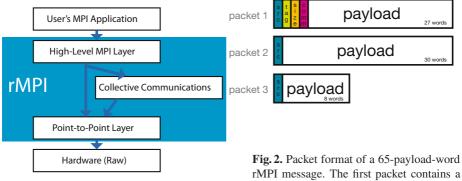

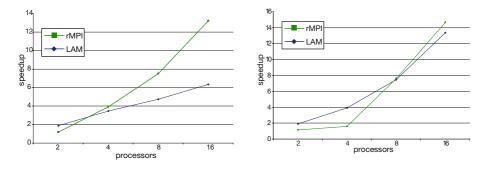

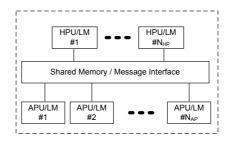

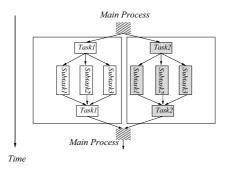

Figure shows rMPI's system architecture. Upon invoking an MPI routine, the user's program calls into the high-level MPI layer, which implements the public MPI API

Fig. 1. The rMPI system architecture

**Fig. 2.** Packet format of a 65-payload-word rMPI message. The first packet contains a full rMPI header, while the later two packets only contain the sender ID.

functions. This layer is responsible for preparing the MPI request for processing by lower layers and handles tasks such as argument checking and data buffer management. This top layer also determines how to best utilize the low level communication routines, and directly invokes them for point-to-point communication. The point-to-point layer implements basic communication primitives through which all communication takes place. This layer interacts directly with Raw's hardware mechanisms, including reading and writing from the GDN network ports. The collective communication layer is invoked by the high-level MPI layer for collective communications operations. This layer implements high-level collective communication algorithms such as broadcast and scatter/gather, and ultimately also calls down into the point-to-point layer for communication. The high-level MPI layer and collective communication layer leverage some of the code base from the LAM/MPI implementation, although much of it was re-implemented for rMPI.

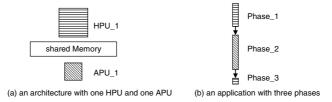

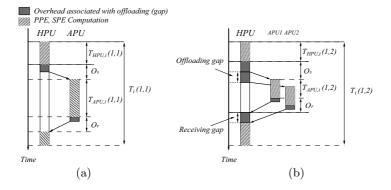

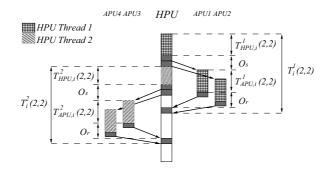

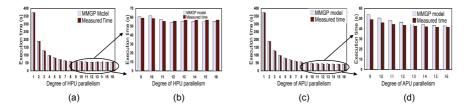

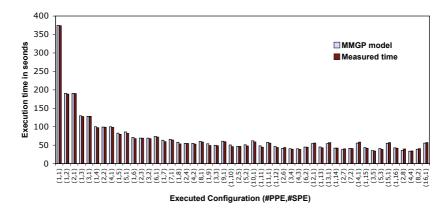

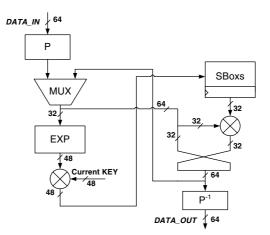

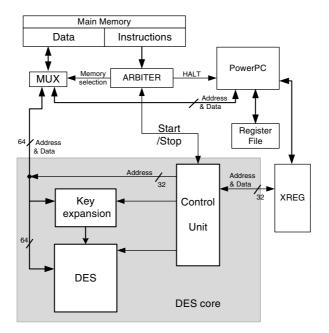

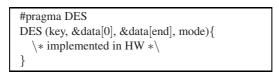

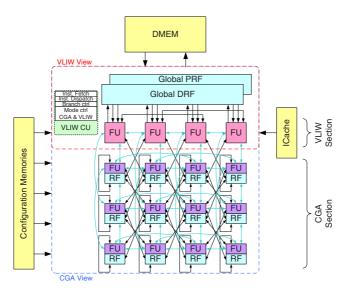

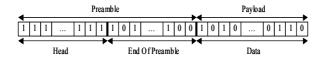

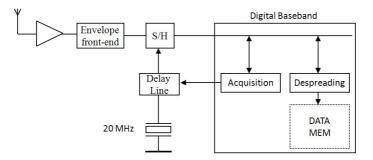

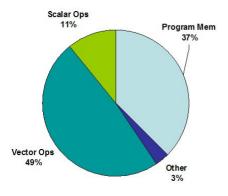

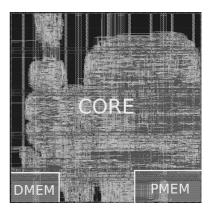

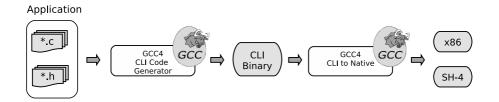

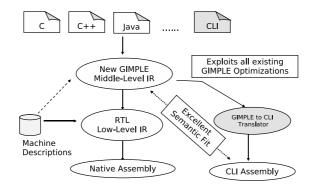

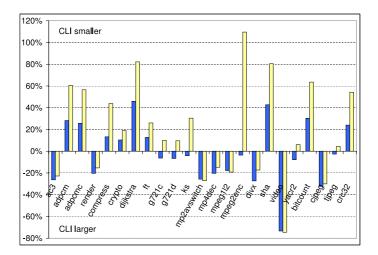

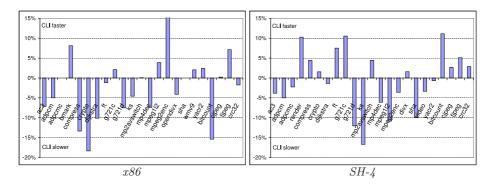

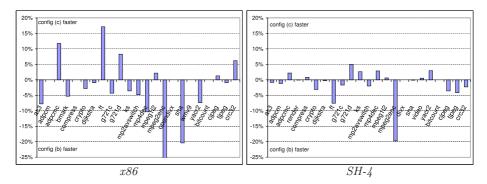

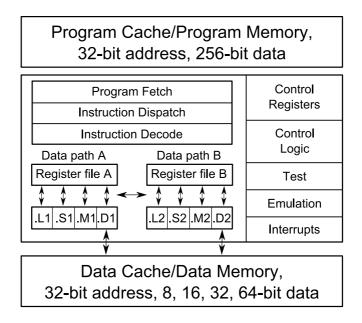

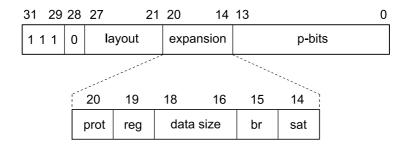

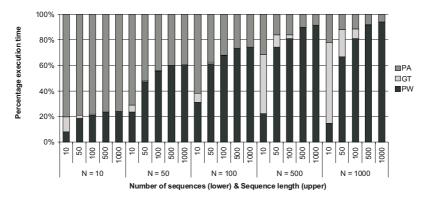

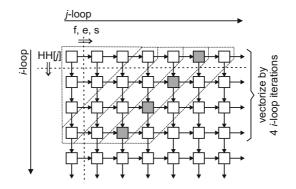

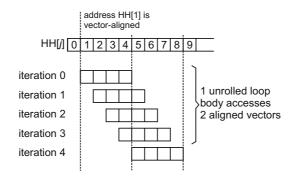

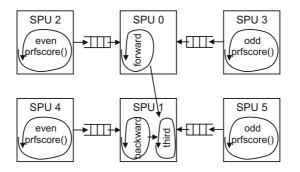

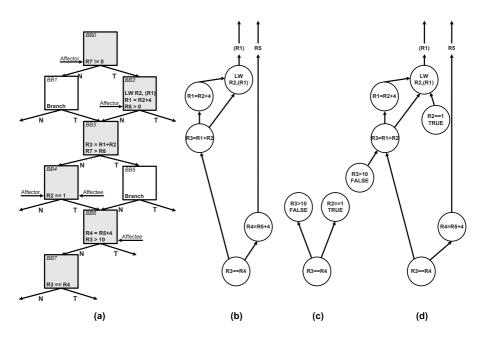

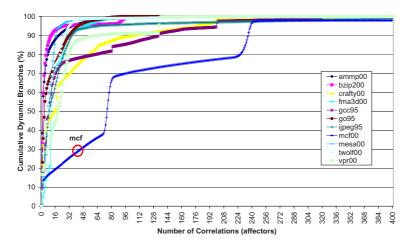

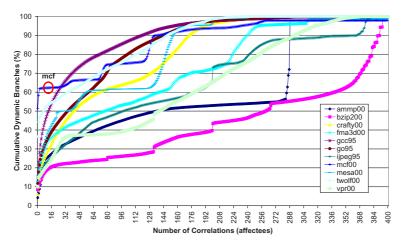

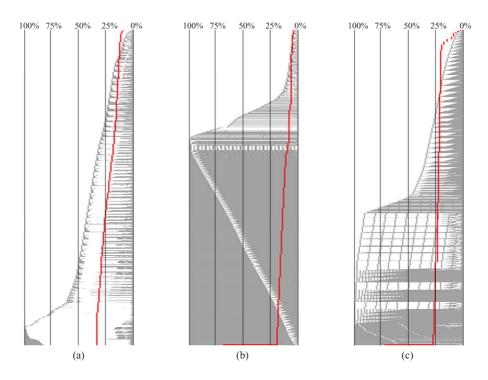

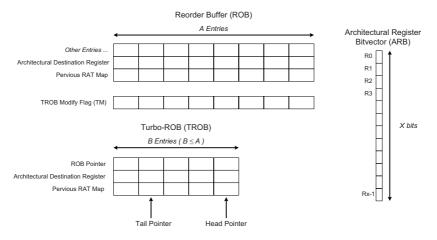

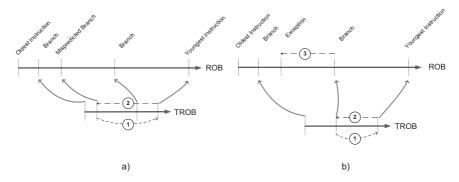

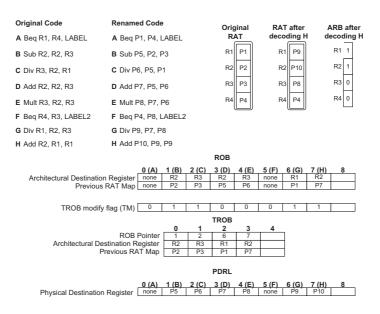

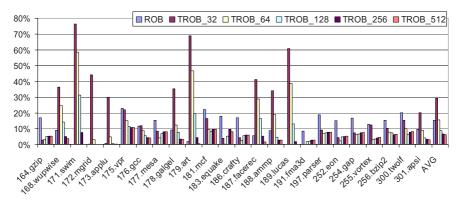

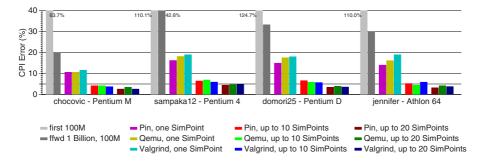

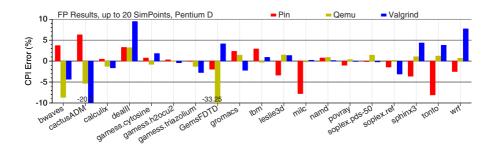

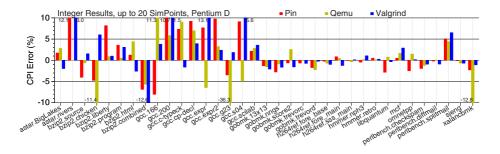

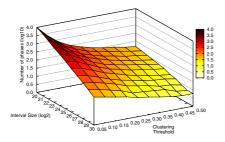

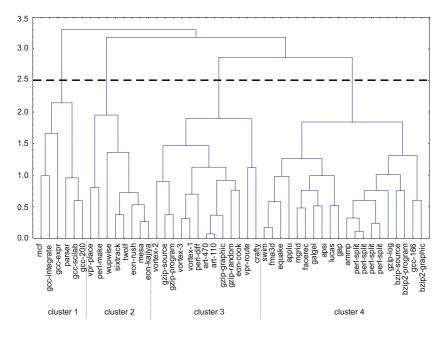

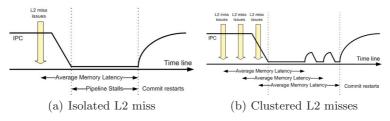

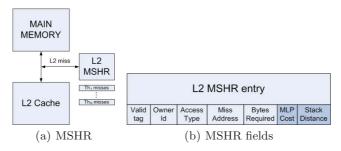

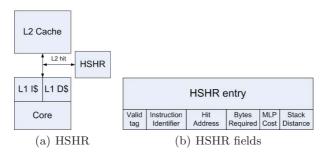

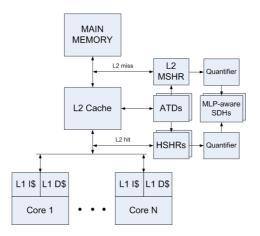

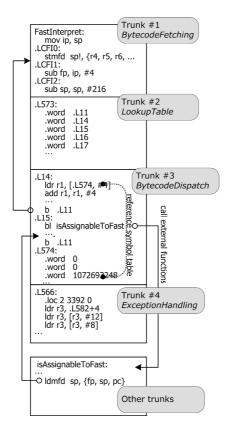

The collective communications layer implements high-level communication primitives such as broadcast and scatter/gather. This layer is called directly by the user program, and ultimately performs the communication operations by calling into the point-to-point layer. More implementation detail can be found in [25].